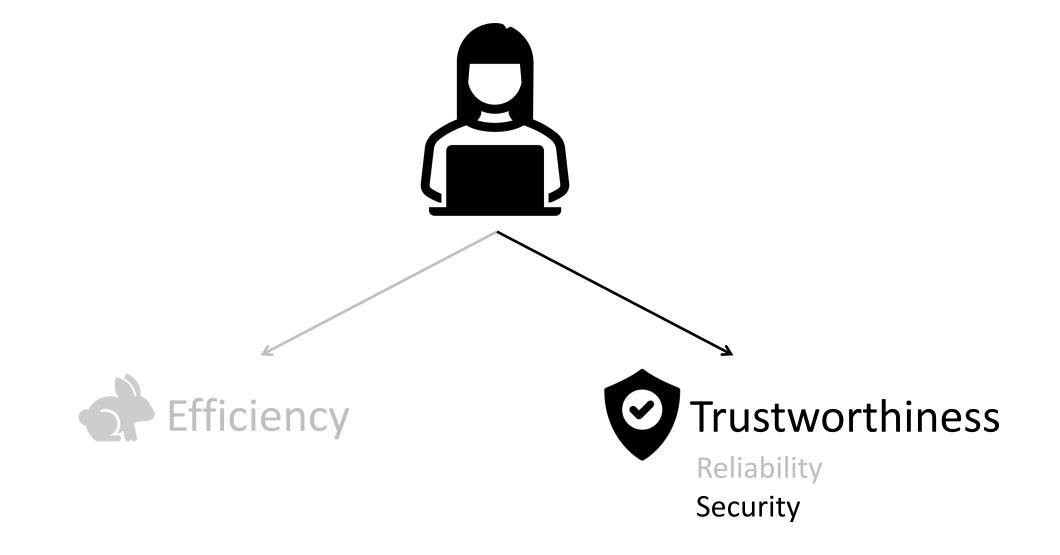

# The Quest for Efficient and Trustworthy Systems

Baris Kasikci

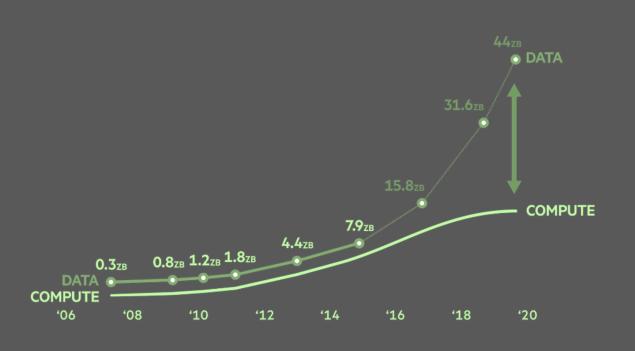

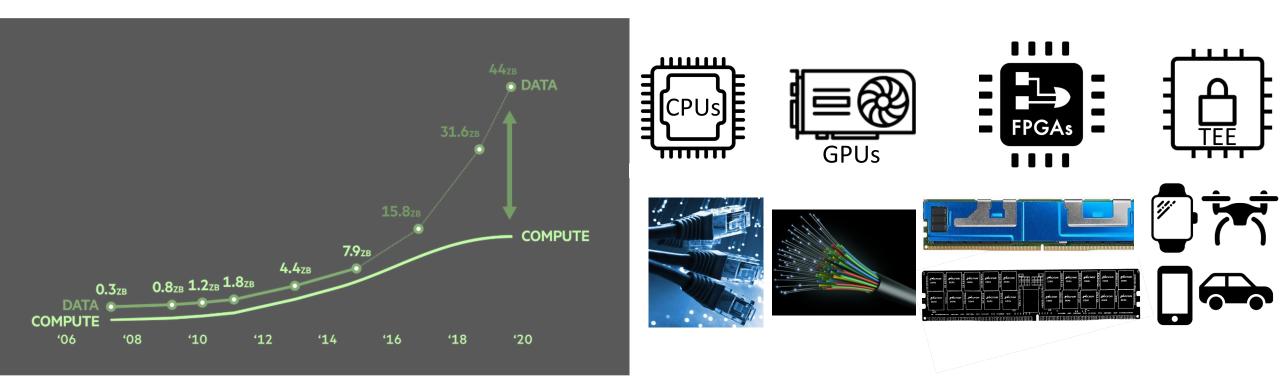

Every 2 years, we create 2x more data than what we have created in all of human history<sup>1</sup>

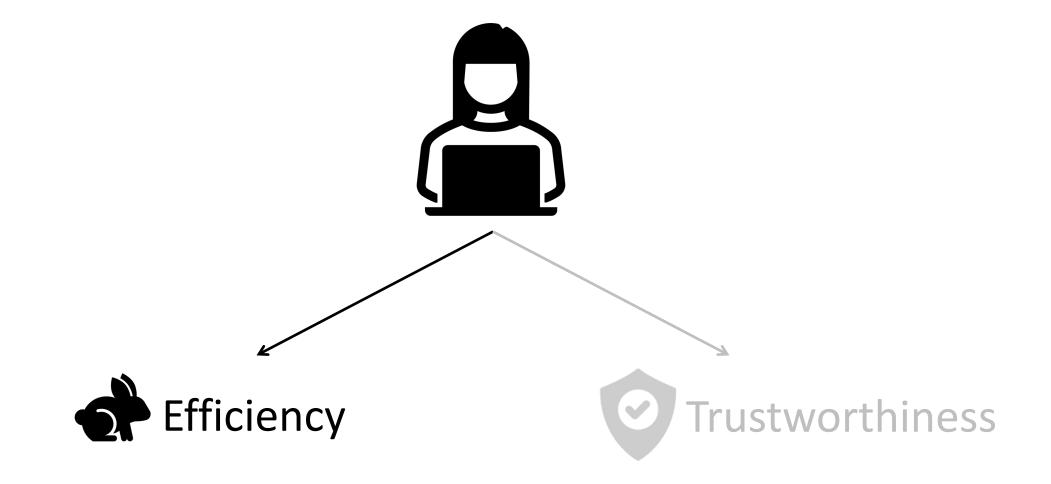

# Efficiency of computer systems needs to catch up

[1] Kirk Bresniker, World Economic Forum, 2018

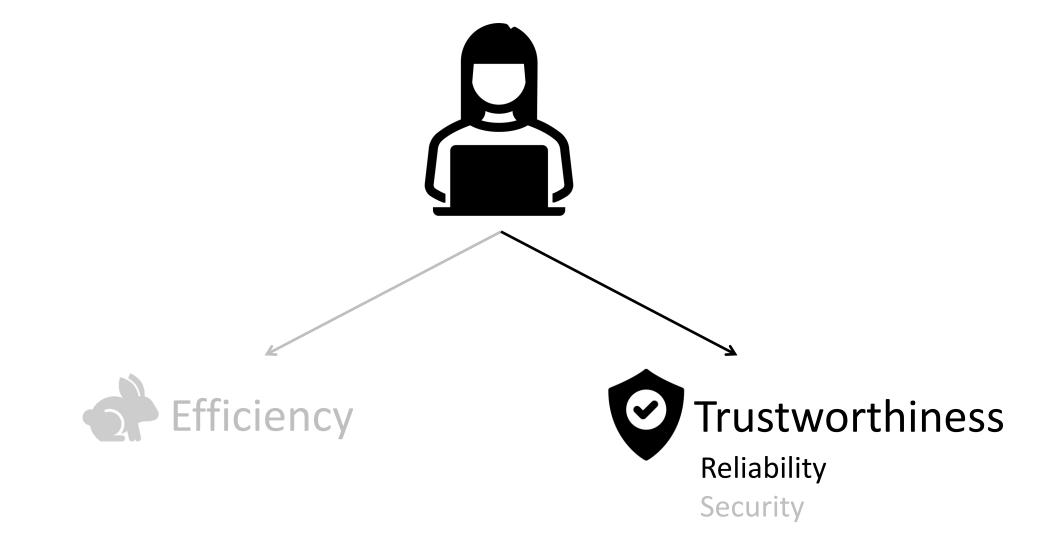

## Total cost of poor software quality > \$2 Trillion in the US<sup>2</sup>

## Trustworthiness (Reliability + Security) needs to improve

[2] Consortium for Information & Software Quality, 2021 Report 3

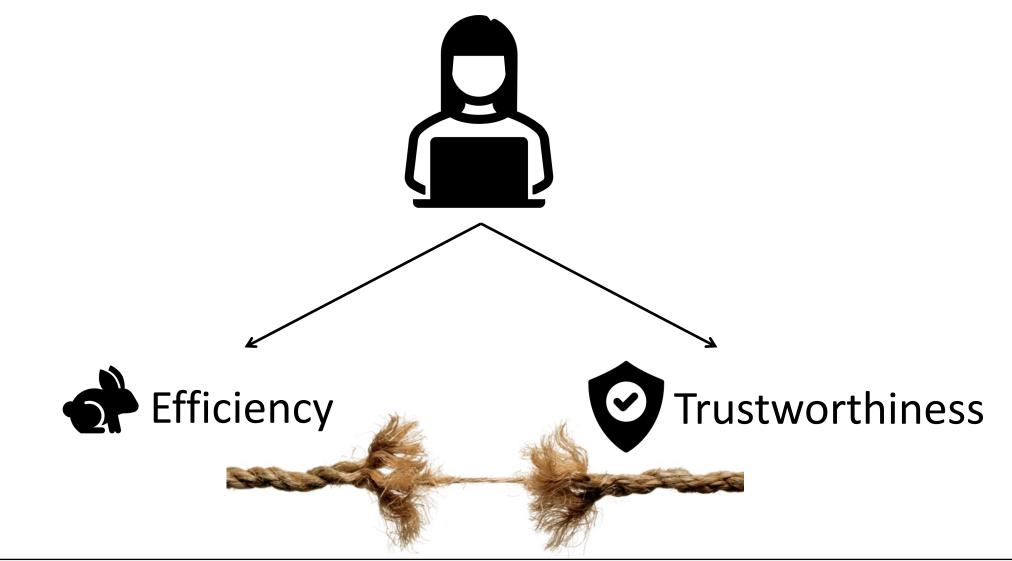

### My Approach

- Designing efficient and trustworthy systems

- based on a systematic understanding of program behavior

| Efficiency                                                         | Trustworthiness                                                 |

|--------------------------------------------------------------------|-----------------------------------------------------------------|

| Datacenter Efficiency<br>Whisper [MICRO'22] Thermometer [IS0       | CA'22] Failure Reproduction and Analysis<br>OmniTable [OSDI'22] |

| Twig [MICRO'21] PDede [MICRO'2<br>DMon [OSDI'21] I-SPY [MICRO'20]  | ER [PLDI'21] REPT [OSDI'18] Snorlax [SOSP'17]                   |

| Heterogeneous Systems Suppo<br>Persistent Memory Indexing [FAST'21 |                                                                 |

| Optimus [ASPLOS'20] Systems Security                               | Hardware Security<br>MOESI-prime [ISCA'22]                      |

| Architecture PL My work app<br>in major ven<br>in all these a      | nues                                                            |

5

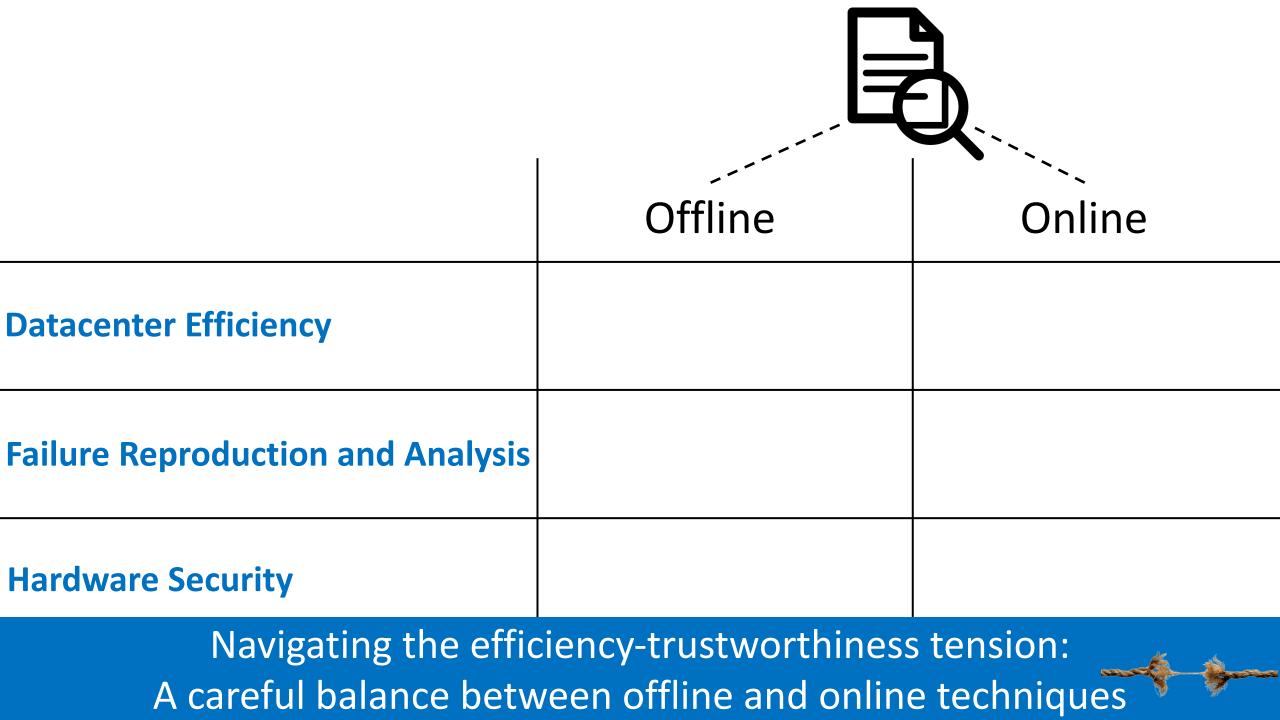

# Outline

|                                   | Offline                      | Online                   |

|-----------------------------------|------------------------------|--------------------------|

| Datacenter Efficiency             | Data-driven<br>optimizations | Lightweight<br>profiling |

| Failure Reproduction and Analysis |                              |                          |

| Hardware Security                 |                              |                          |

### Datacenters consume massive energy

- 3% of the global energy, large carbon footprint<sup>1</sup>

- \$35 million/year savings from 1% less work<sup>2</sup>

### **Responsiveness impacts revenue**

- 400ms delay decreases Google Search users by 0.4%<sup>2</sup>

- Two second delay on search responses reduces Microsoft Bing's revenue by 4.3%<sup>2</sup>

[1] Rano Danilak, Why Energy Is A Big And Rapidly Growing Problem For Data Centers?, 2017[2] Kathryn McKinley , Tail Latency: Beyond Queuing Theory, 2017

Google

#### AutoFDO: Automatic Feedback-Directed Optimization for Warehouse-Scale Applications

Dehao Chen Google Inc. dehao@google.com David Xinliang Li Google Inc. davidxl@google.com Tipp Moseley Google Inc. tipp@google.com

#### BOLT: A Practical Binary Optimizer for Data Centers and Beyond

Maksim Panchenko, Rafael Auler, Bill Nell, Guilherme Ottoni Facebook, Inc. Menlo Park, CA, USA {maks,rafaelauler,bnell,ottoni}@fb.com

Vulcan

Binary transformation in a distributed environment

Amitabh Srivastava

Andrew Edwards

Hoi Vo

### **Profile-Guided Optimizations, PGO** e.g., use a profile of branch traces for reordering code to make it cache-friendly

**Cooperative Prefetching: Compiler and Hardware Support for Effective Instruction Prefetching in Modern Processors**

Chi-Keung Luk Temporal Instruction Fetch Streaming

# Limitations: Significant hardware modifications Impractical on-chip space overhead Limited gains due to on-chip space limits

# Lawrence Sp Lawrence Sp

Rakesh Kumar<sup>\*</sup> Uppsala University Boris Grot University of Edinburgh Vijay Nagarajan University of Edinburgh 11

### Profile-Guided Software Optimizations

### On-Chip Analysis and Optimizations

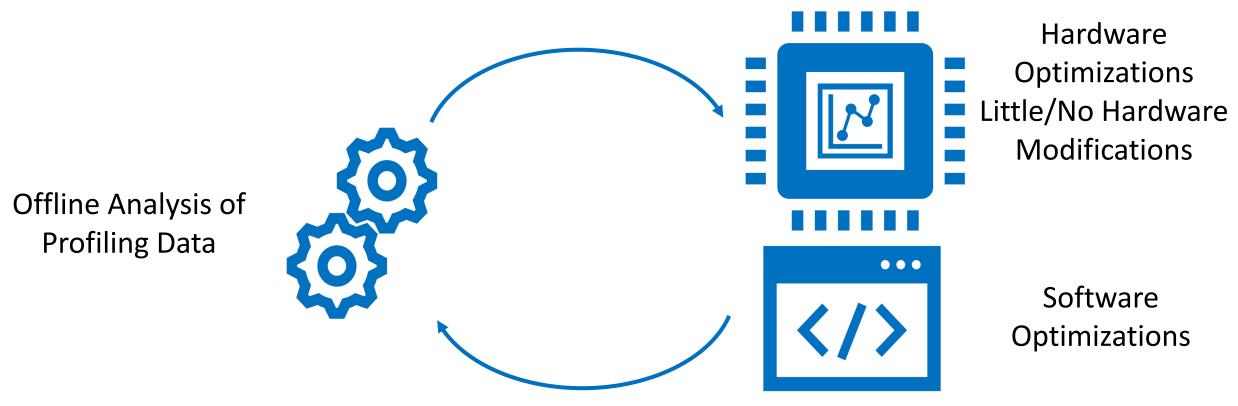

### Profile-Guided Software and Hardware Optimizations

**Online Lightweight Profiling**

## Profile-Guided Software and Hardware Optimizations

**Online Lightweight Profiling**

Performance improvement of up to 90% of the theoretical limit Little-to-No hardware modifications (Intel & ARM technology transfer)

# I-SPY: Context-Driven Conditional Instruction Prefetching with Coalescing

Tanvir Ahmed Khan<sup>\*</sup> Akshitha Sriraman<sup>\*</sup> Joseph Devietti<sup>†</sup> Gilles Pokam<sup>‡</sup> Heiner Litz<sup>§</sup> Baris Kasikci<sup>\*</sup> <sup>\*</sup>University of Michigan <sup>†</sup>University of Pennsylvania <sup>‡</sup>Intel Corporation <sup>§</sup>University of California, Santa Cruz <sup>\*</sup>{takh, akshitha, barisk}@umich.edu <sup>†</sup>devietti@cis.upenn.edu <sup>‡</sup>gilles.a.pokam@intel.com <sup>§</sup>hlitz@ucsc.edu

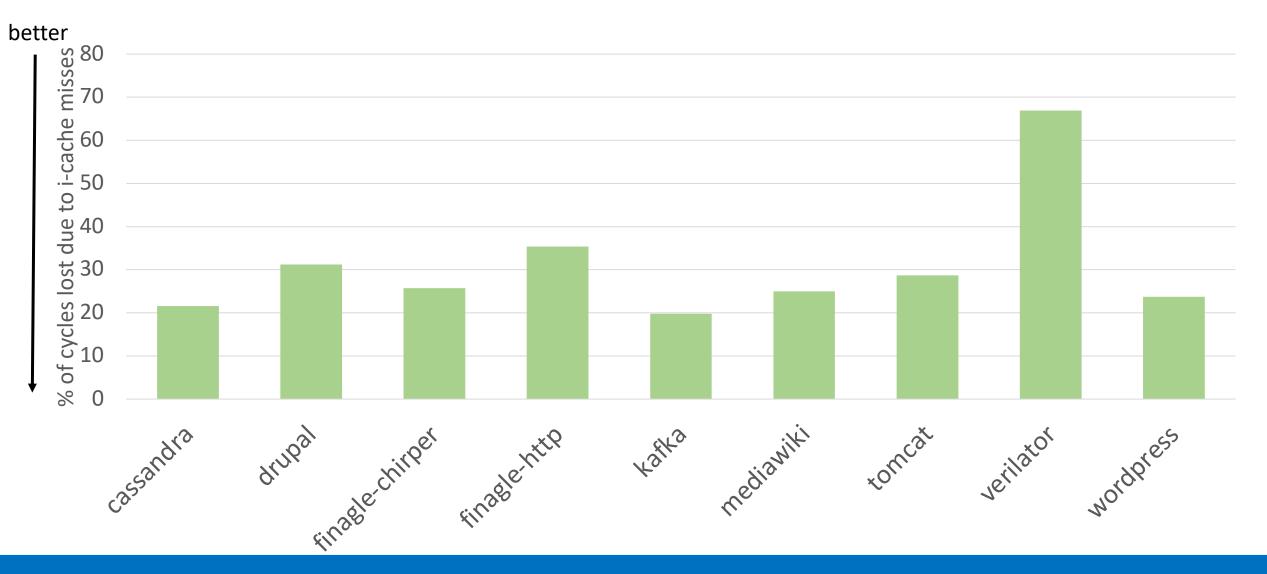

# Performance Impact of Instruction Cache Misses

20-70% performance lost due to large instruction footprint (14-45x l-cache)

16

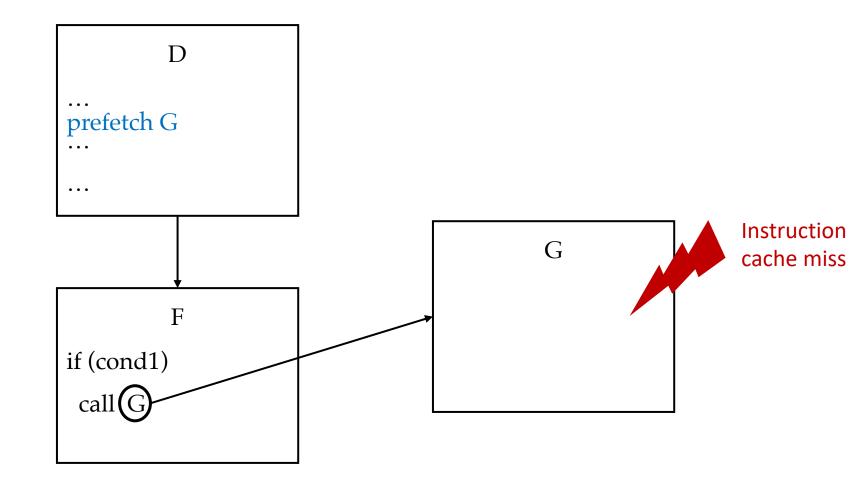

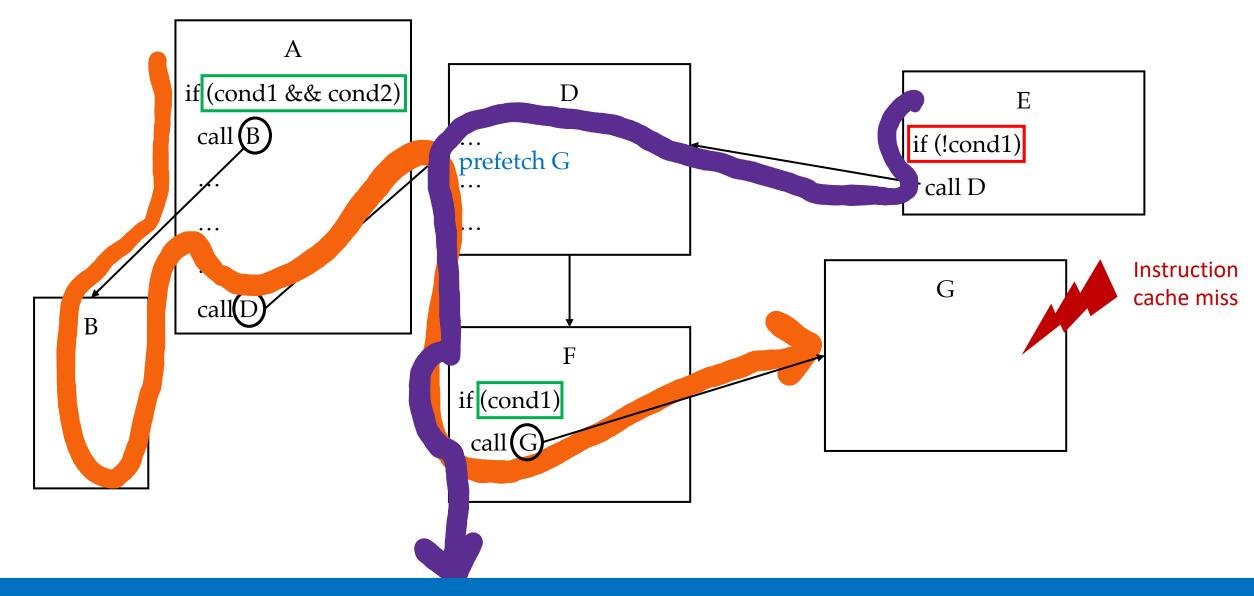

# Why Does Prior Work Fall Short?

Why Does Prior Work Fall Short?

Overfitting prefetches based on limited execution information hurts speedup

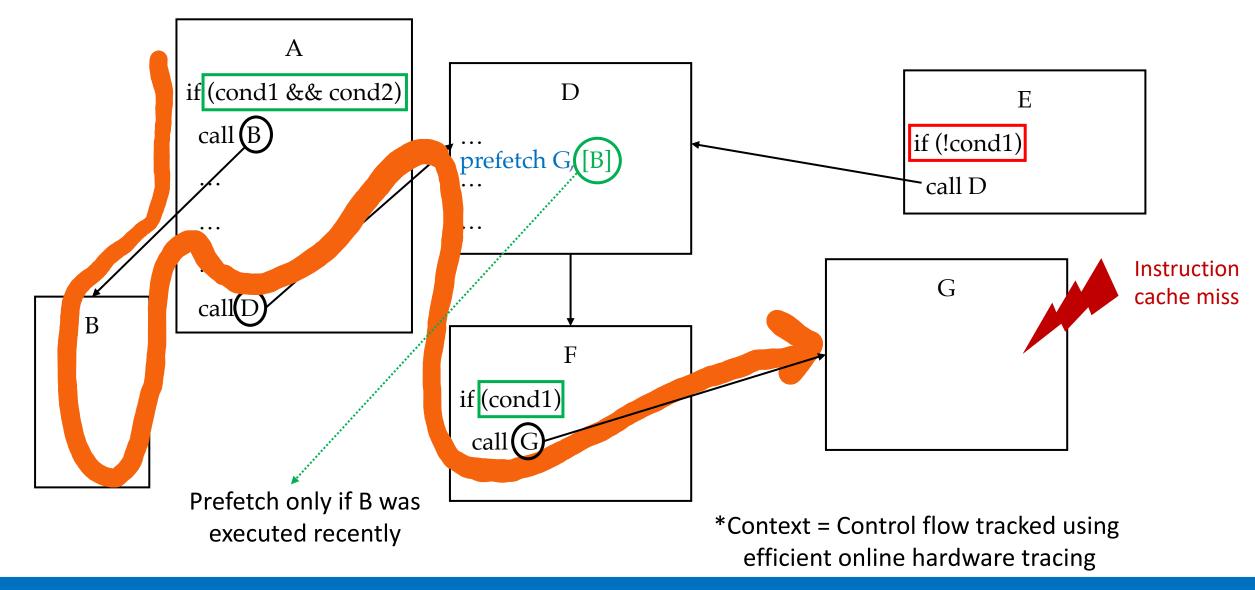

# Context-Driven\* Conditional Prefetching

4 branches-long context information allows 90% of the speed of an ideal cache

### I-SPY

### **Context-Driven Conditional Prefetching**

- A data-driven optimization powered by offline analysis of profiling information

- Avoids unnecessary prefetches

- Can be implemented with minor hardware support

- Achieves 90% of the ideal cache performance

- Outperforms prior work by Google by 22.5%

$\rightarrow$  ~ \$700 million in savings<sup>1</sup>

#### **ISCA'22**

#### **Thermometer: Profile-Guided BTB Replacement for Data Center Applications.**

Shixin Song shixins@umich.edu University of Michigan, USA

Tanvir Ahmed Khan takh@umich.edu University of Michigan, USA

Sara Mahdizadeh Shahri smahdiz@umich.edu University of Michigan, USA

Sreenivas Subramoney

Intel Labs, India

Akshitha Sriraman akshitha@cmu.edu Carnegie Mellon University, USA

Niranjan Soundararajan niranjan.k.soundararajan@intel.com sreenivas.subramoney@intel.com Intel Labs, India

Heiner Litz hlitz@ucsc.edu University of California, Santa Cruz, USA

Baris Kasikci barisk@umich.edu University of Michigan, USA

#### **MICRO'22**

#### Whisper: Profile-Guided Branch Misprediction Elimination for Data Center Applications

Tanvir Ahmed Khan\* Muhammed Ugur\* Krishnendra Nathella<sup>†</sup> Dam Sunwoo<sup>†</sup> Heiner Litz<sup>‡</sup> Daniel A. Jiménez<sup>§</sup> Baris Kasikci<sup>\*</sup> \*University of Michigan <sup>†</sup>ARM <sup>‡</sup>University of California, Santa Cruz <sup>§</sup>Texas A&M University \*{takh, meugur, barisk}@umich.edu <sup>†</sup>{Krishnendra.Nathella, Dam.Sunwoo}@arm.com <sup>‡</sup>hlitz@ucsc.edu <sup>§</sup>diimenez@acm.org

#### **MICRO'22**

#### **OCOLOS:** Online COde Layout OptimizationS

Yuxuan Zhang\* Tanvir Ahmed Khan<sup>†</sup> Gilles Pokam<sup>‡</sup> Baris Kasikci<sup>†</sup> Heiner Litz<sup>§</sup> Joseph Devietti<sup>\*</sup> \*University of Pennsylvania <sup>†</sup>University of Michigan <sup>‡</sup>Intel Corporation <sup>§</sup>University of California, Santa Cruz <sup>†</sup>{takh, barisk}@umich.edu \*{zyuxuan, devietti}@seas.upenn.edu <sup>‡</sup>gilles.a.pokam@intel.com <sup>§</sup>hlitz@ucsc.edu

#### EuroSys'22 **APT-GET:** Profile-Guided Timely Software Prefetching

Saba Jamilan<sup>\*</sup> Tanvir Ahmed Khan<sup>‡</sup> Grant Ayers<sup>†</sup> Baris Kasikci<sup>‡</sup> Heiner Litz<sup>\*</sup> \*University of California, Santa Cruz <sup>†</sup>Google <sup>‡</sup>University of Michigan

#### **OSDI'21**

DMon: Efficient Detection and Correction of Data Locality Problems Using **Selective Profiling**

Tanvir Ahmed Khan University of Michigan

Ian Neal Gilles Pokam University of Michigan Intel Corporation

Barzan Mozafari University of Michigan

Baris Kasikci

University of Michigan

#### **ISCA'21**

Ripple: Profile-Guided Instruction Cache **Replacement for Data Center Applications**

Tanvir Ahmed Khan\* Dexin Zhang<sup>†</sup> Akshitha Sriraman\* Joseph Devietti<sup>‡</sup> Gilles Pokam<sup>§</sup> Heiner Litz<sup>¶</sup> Baris Kasikci<sup>\*</sup> <sup>†</sup>University of Science and Technology of China <sup>‡</sup>University of Pennsylvania \*University of Michigan <sup>§</sup>Intel Corporation <sup>¶</sup>University of California, Santa Cruz \*{takh, akshitha, barisk}@umich.edu <sup>†</sup>zhangdexin@mail.ustc.edu.cn <sup>‡</sup>devietti@cis.upenn.edu <sup>§</sup>gilles.a.pokam@intel.com <sup>¶</sup>hlitz@ucsc.edu

#### MICRO'21

#### **Twig: Profile-Guided BTB Prefetching for Data Center** Applications

Tanvir Ahmed Khan takh@umich.edu University of Michigan, USA

Nathan Brown nlbrow@umich.edu University of Michigan, USA

Akshitha Sriraman akshitha@umich.edu University of Michigan, USA

Joseph Devietti

devietti@cis.upenn.edu

University of Pennsylvania, USA

Niranjan Soundararajan niranjan.k.soundararajan@intel.com Intel Labs, India

Rakesh Kumar rakesh.kumar@ntnu.no Norwegian University of Science and Technology, Norway

Sreenivas Subramoney sreenivas.subramonev@intel.com Intel Labs, India

Gilles Pokam gilles.a.pokam@intel.com Intel Labs, USA

Heiner Litz hlitz@ucsc.edu University of California, Santa Cruz, USA

Baris Kasikci barisk@umich.edu University of Michigan, USA

#### **MICRO'21** PDede: Partitioned, Deduplicated, Delta Branch Target Buffer

Niranjan Soundararajan niranjan.k.soundararajan@intel.com Processor Architecture Research Lab. Intel Labs, India

Peter Braun pvbraun@ucsc.edu University of California, Santa Cruz USA

takh@umich.edu University of Michigan USA

Tanvir Ahmed Khan

Baris Kasikci barisk@umich.edu University of Michigan USA

Heiner Litz hlitz@ucsc.edu University of California, Santa Cruz USA

Sreenivas Subramonev sreenivas.subramoney@intel.com Processor Architecture Research Lab Intel Labs, India

Datacenter Efficiency Thermometer [ISCA'22] Twig [MICRO'21] PDede [MICRO'21] DMon [OSDI'21] I-SPY [MICRO'20] Ripple [ISCA'21] Huron [PLDI'19] Cntr [ATC'18]

### Awards

VMware Early Career Grant Intel Rising Star Award Intel Faculty Awards

• 2017, 2018

Rackham Ph.D. Fellowship

Tanvir Ahmed Khan

MICRO'22 Best Paper Award

### Grants

• NSF, Intel, SRC

Intel<sup>1</sup> and ARM<sup>2</sup> technology transfer

### **Collaborations**

- ARM

- University of Pennsylvania

- UC Santa Cruz

[1] https://patents.google.com/patent/US20210342134A1/en

[2] https://community.arm.com/arm-community-blogs/b/tools-software-ides-blog/posts/arm-neoverse-n1-performance-analysis-methodology 22

# Outline

|                                   | Offline                      | Online                   |

|-----------------------------------|------------------------------|--------------------------|

| Datacenter Efficiency             | Data-driven<br>optimizations | Lightweight<br>profiling |

| Failure Reproduction and Analysis |                              |                          |

| Hardware Security                 |                              |                          |

# Outline

|                                   | Offline                            | Online                              |

|-----------------------------------|------------------------------------|-------------------------------------|

| Datacenter Efficiency             | Data-driven<br>optimizations       | Lightweight<br>profiling            |

|                                   | Static & symbolic                  | Coloctivo                           |

| Failure Reproduction and Analysis | Static & symbolic program analysis | Selective<br>information monitoring |

### Characterizing and Predicting Which Bugs Get Fixed: An Empirical Study of Microsoft Windows

Philip J. Guo\* Thomas Zimmermann<sup>+</sup> Nachiappan Nagappan<sup>+</sup> Brendan Murphy<sup>+</sup> \* Stanford University + Microsoft Research

"Developers can fix a bug if they can reproduce the associated failure"

Reproducing failures is difficult, especially for production use cases

Navigating the efficiency/trustworthiness tension:

29

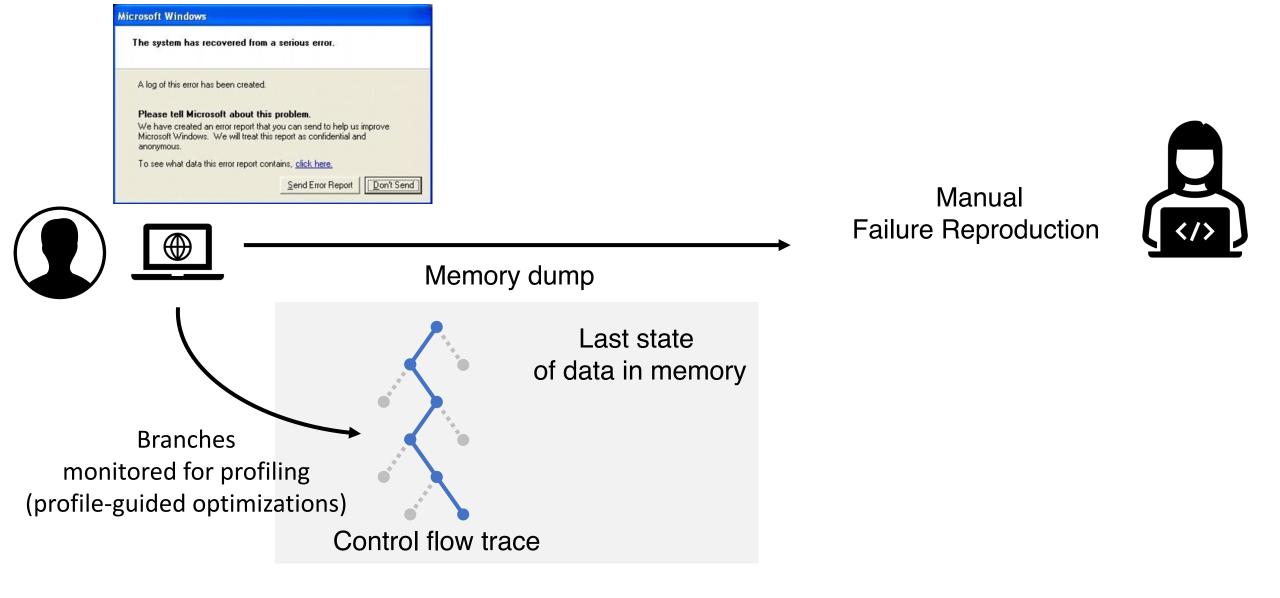

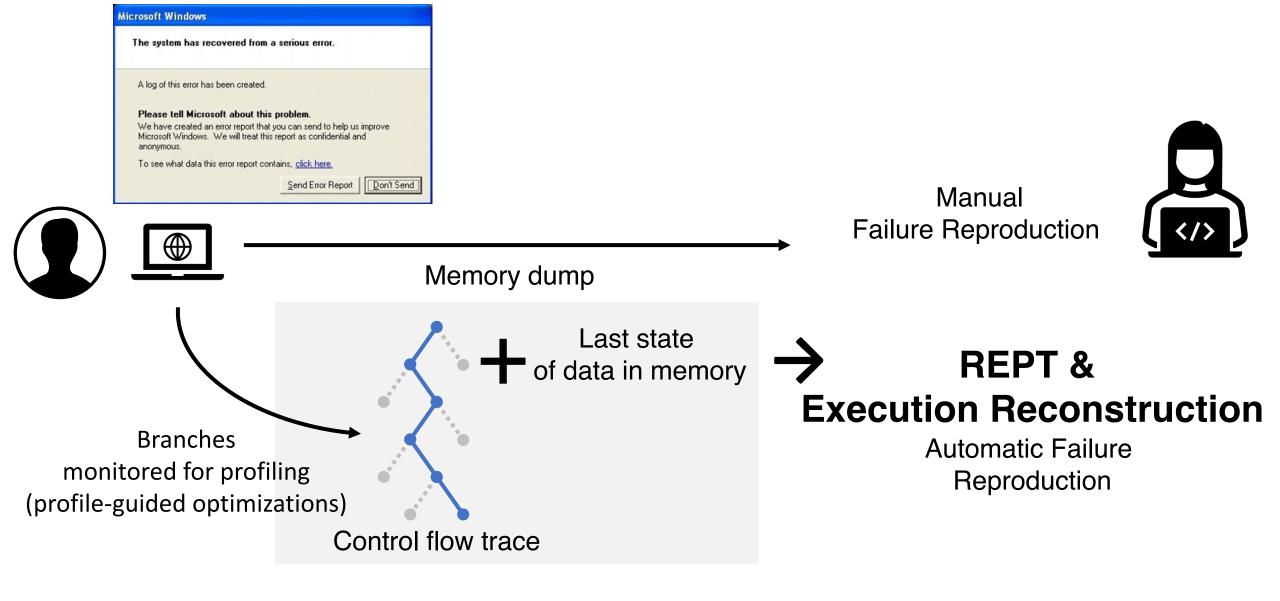

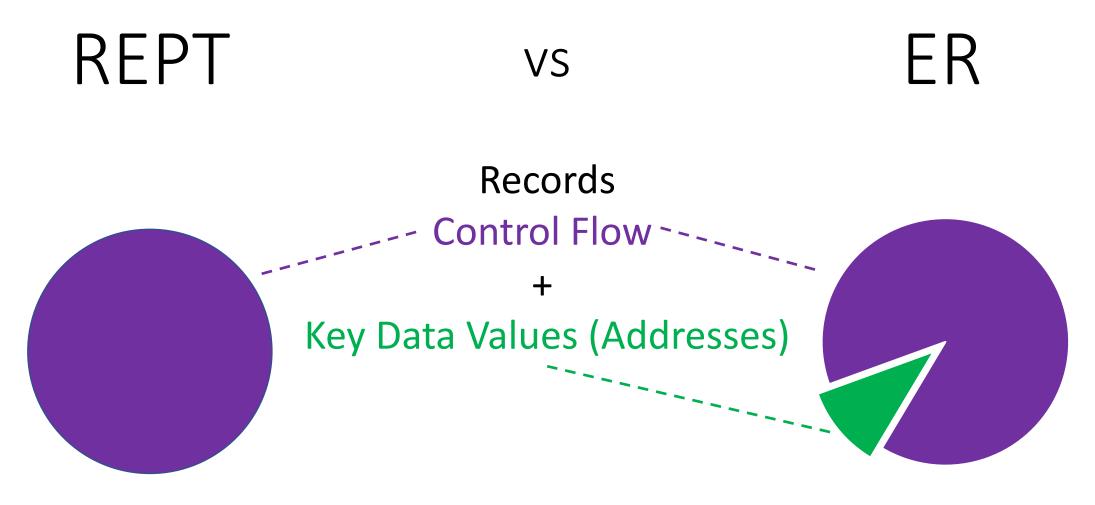

# **REPT** and Execution Reconstruction

REPT: Reverse Debugging of Failures in Deployed Software

- Most-widely deployed failure reproduction and analysis system in the world

- Used in ~ 1 billion Microsoft Windows systems

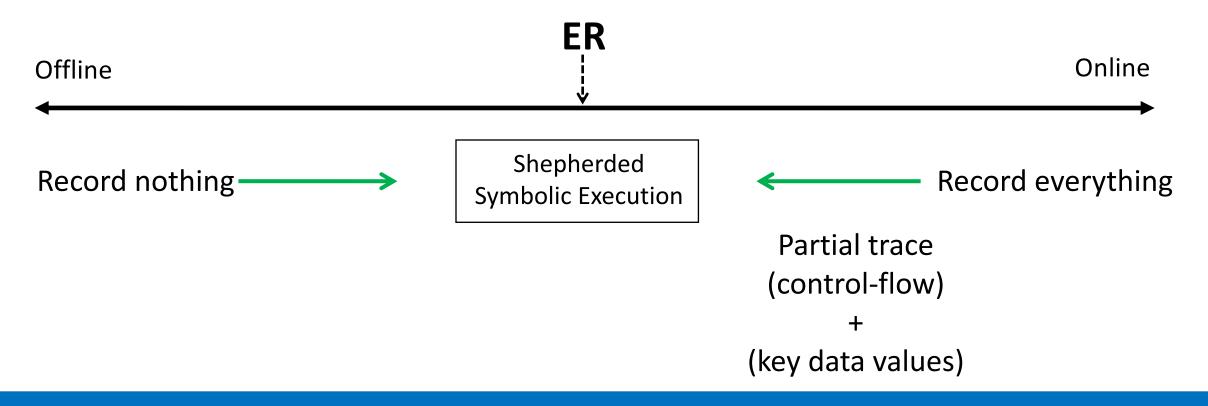

### **Execution Reconstruction (ER)**

- Offline symbolic program analysis

- Online selective hardware monitoring (control and data)

- Reproduces arbitrarily longer executions than what REPT can

**OSDI 2018**

**Best Paper Award**

# **Execution Reconstruction: Harnessing Failure Reoccurrences for Failure Reproduction**

Gefei Zuo gefeizuo@umich.edu University of Michigan, USA

Pramod Bhatotia pramod.bhatotia@in.tum.de TU Munich, Germany Jiacheng Ma jcma@umich.edu University of Michigan, USA

Pedro Fonseca pfonseca@purdue.edu Purdue University, USA Andrew Quinn arquinn@umich.edu University of Michigan, USA

Baris Kasikci barisk@umich.edu University of Michigan, USA

PLDI'2

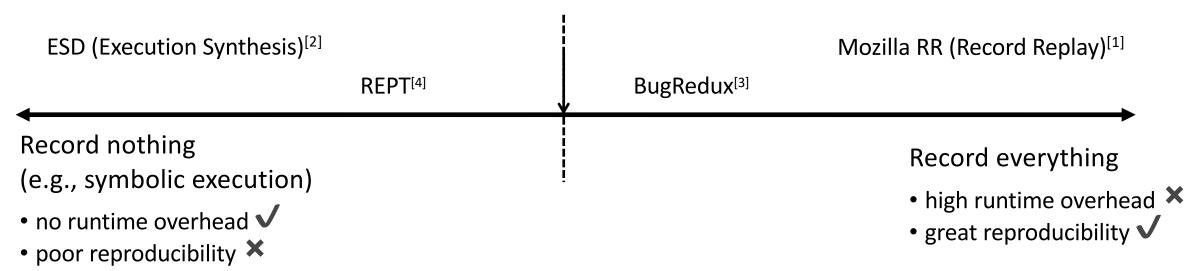

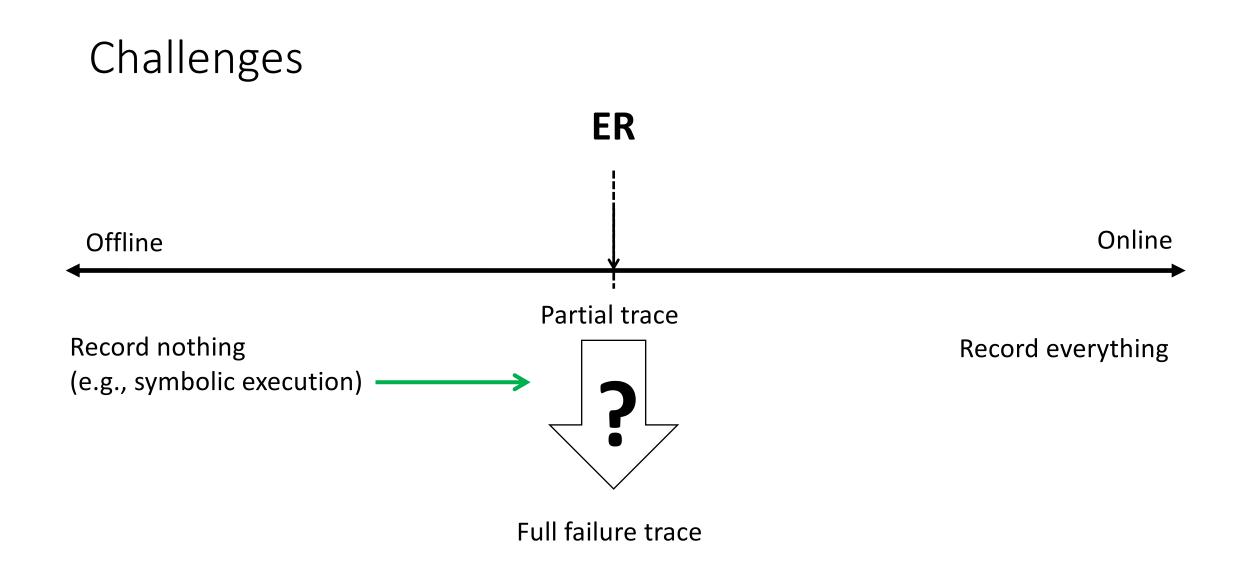

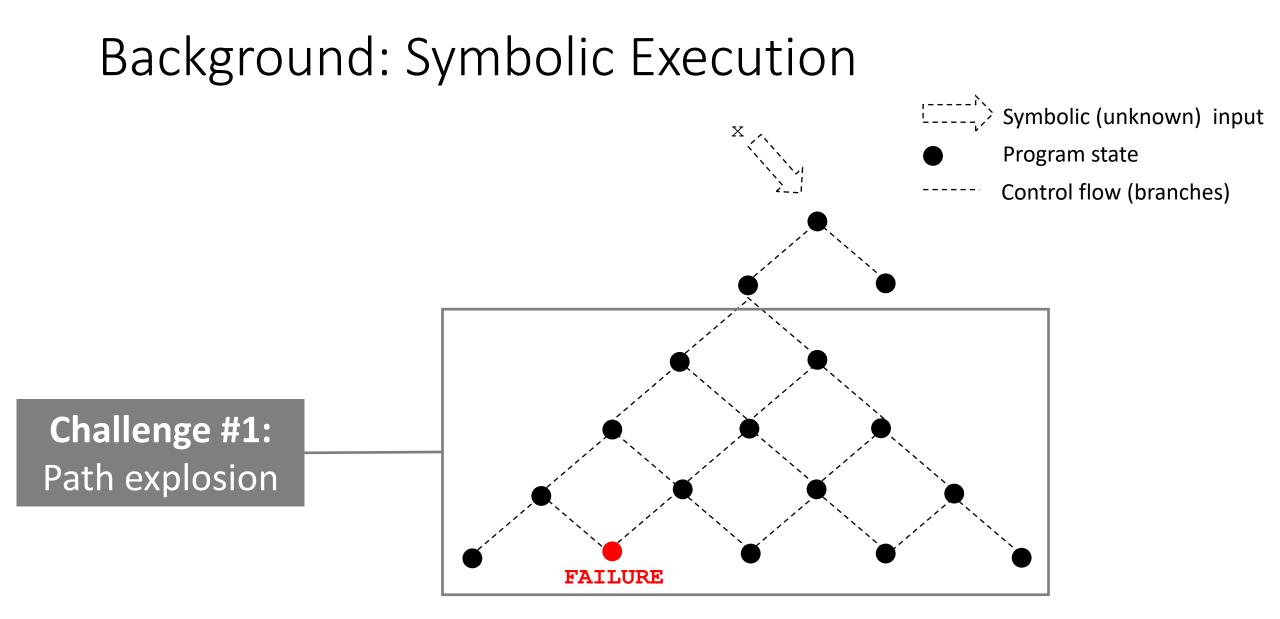

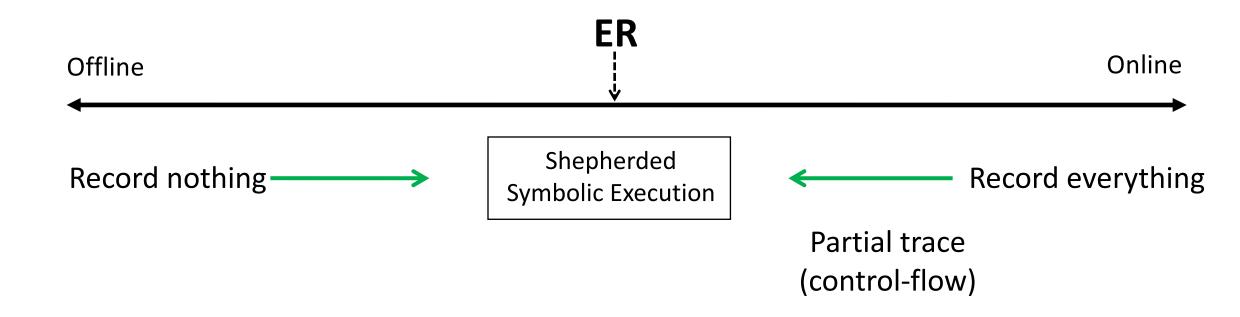

### Prior Work vs. Execution Reconstruction (ER)

### ER (our work)

### Existing trade-offs are insufficient to reproduce complex production failures

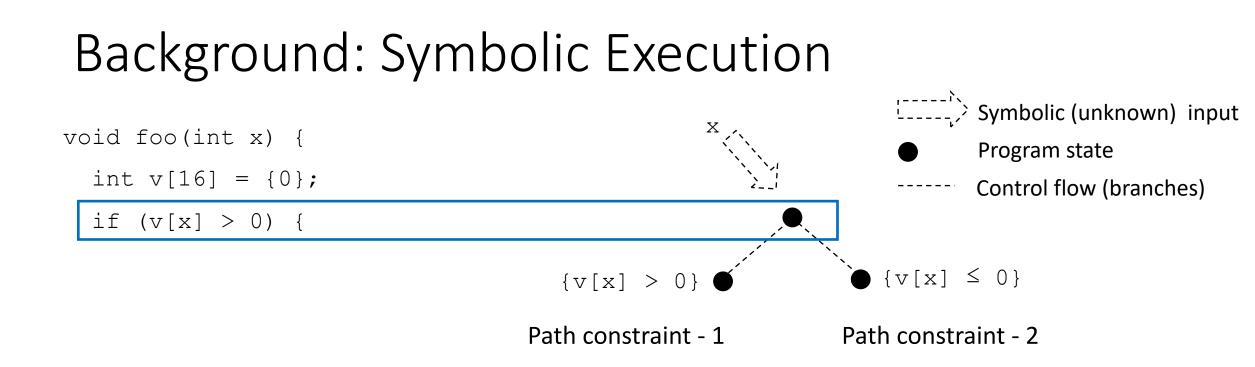

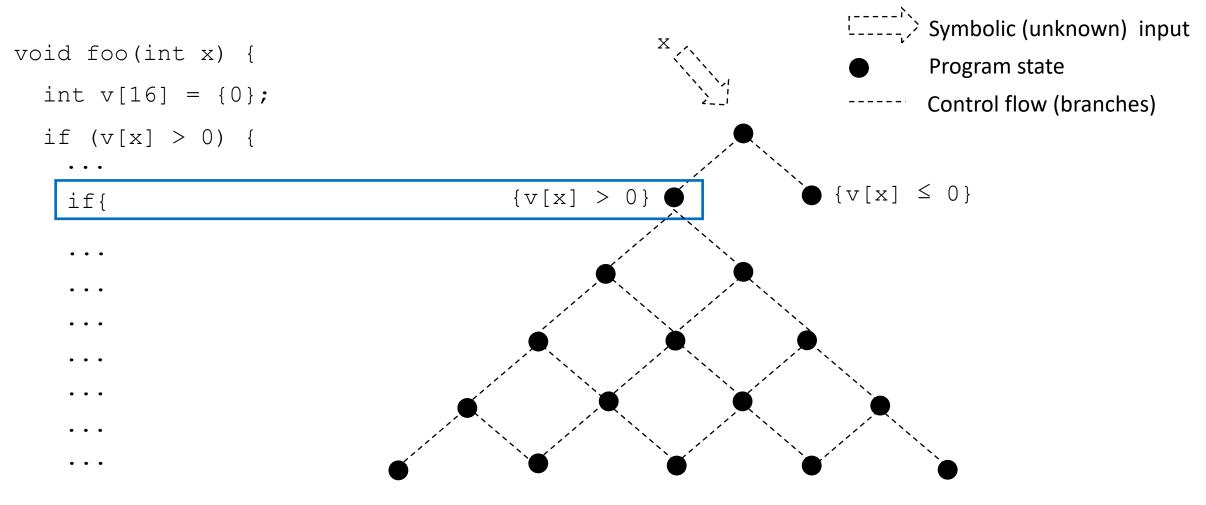

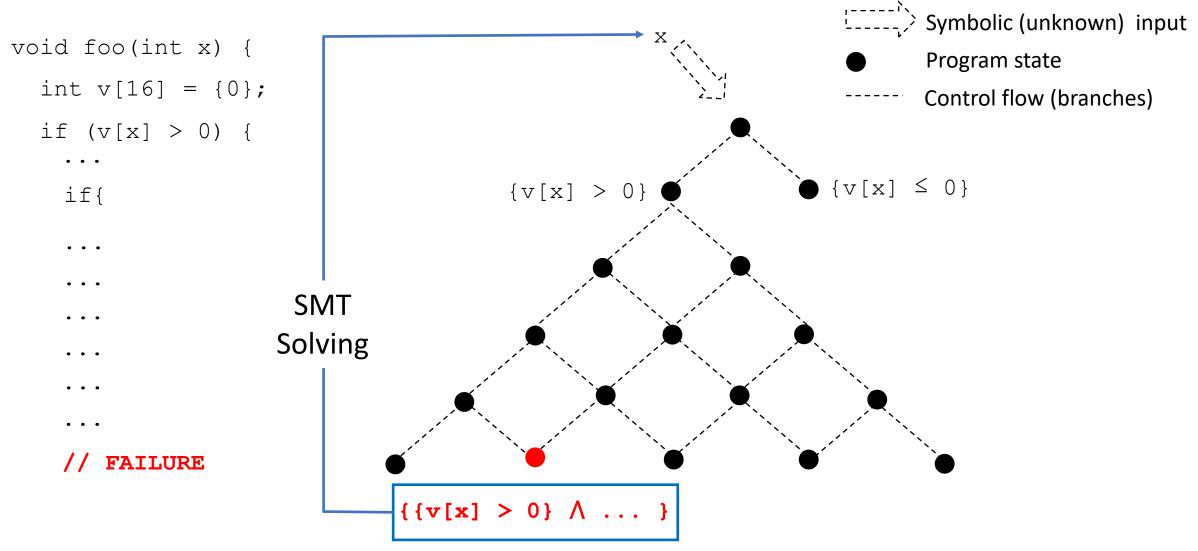

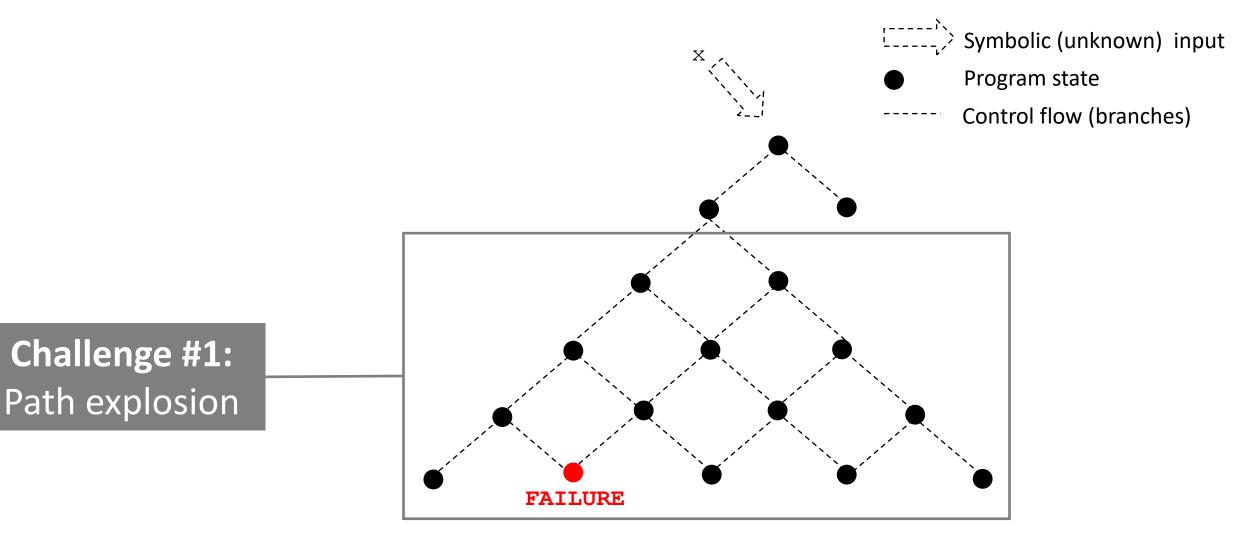

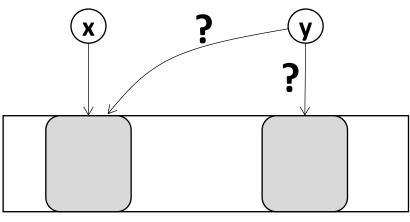

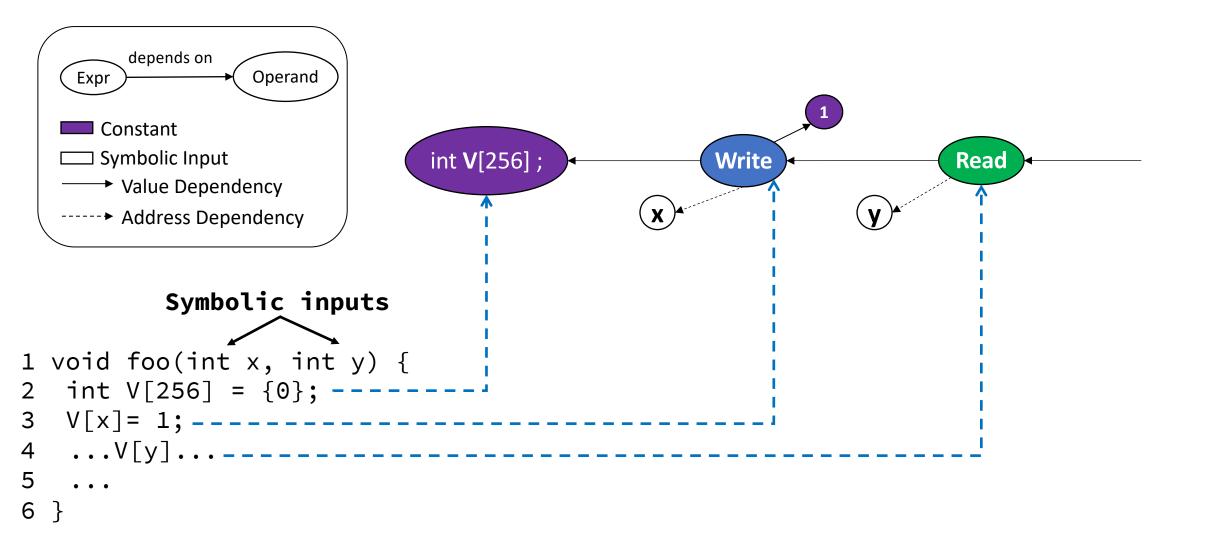

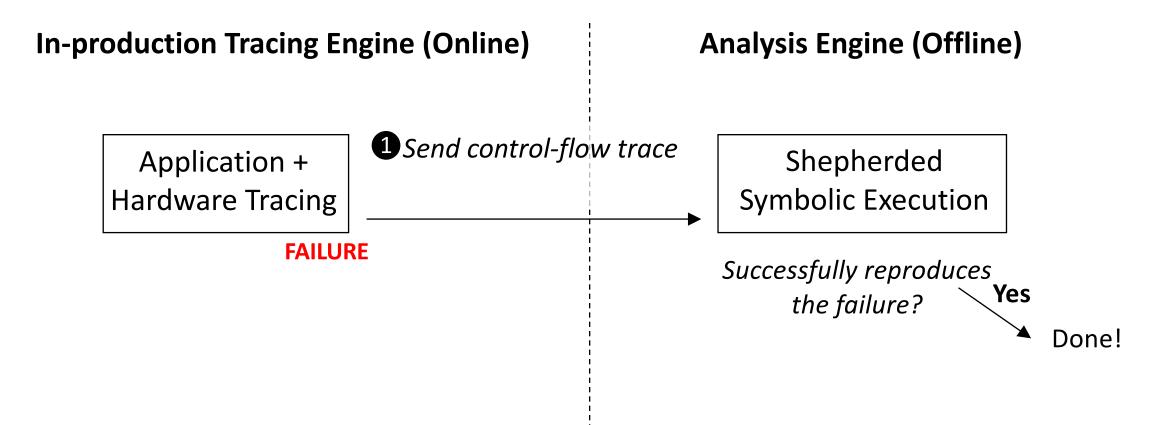

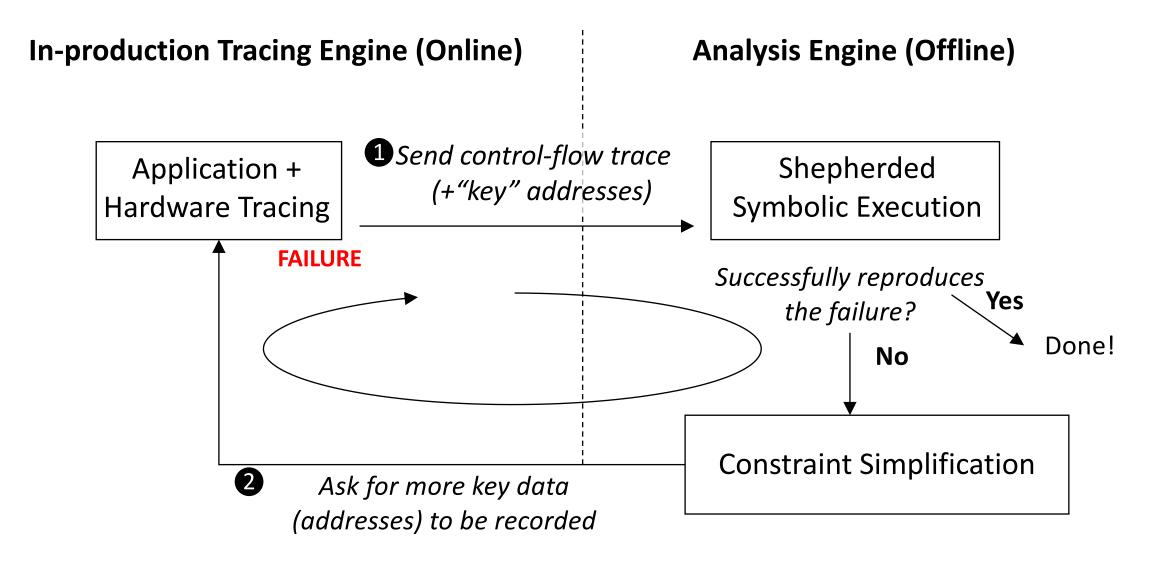

# Background: Symbolic Execution

# Background: Symbolic Execution

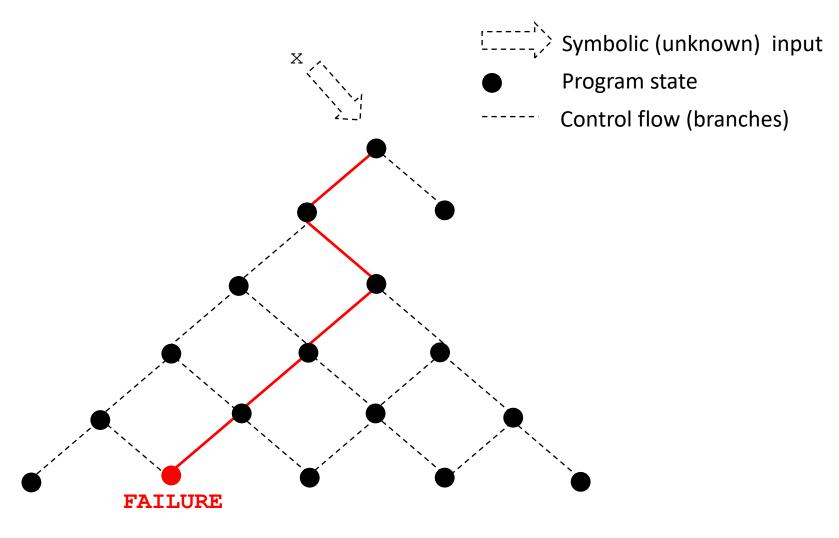

• Avoids path-explosion by following a control flow trace recorded in production

# SMT Solving is Difficult

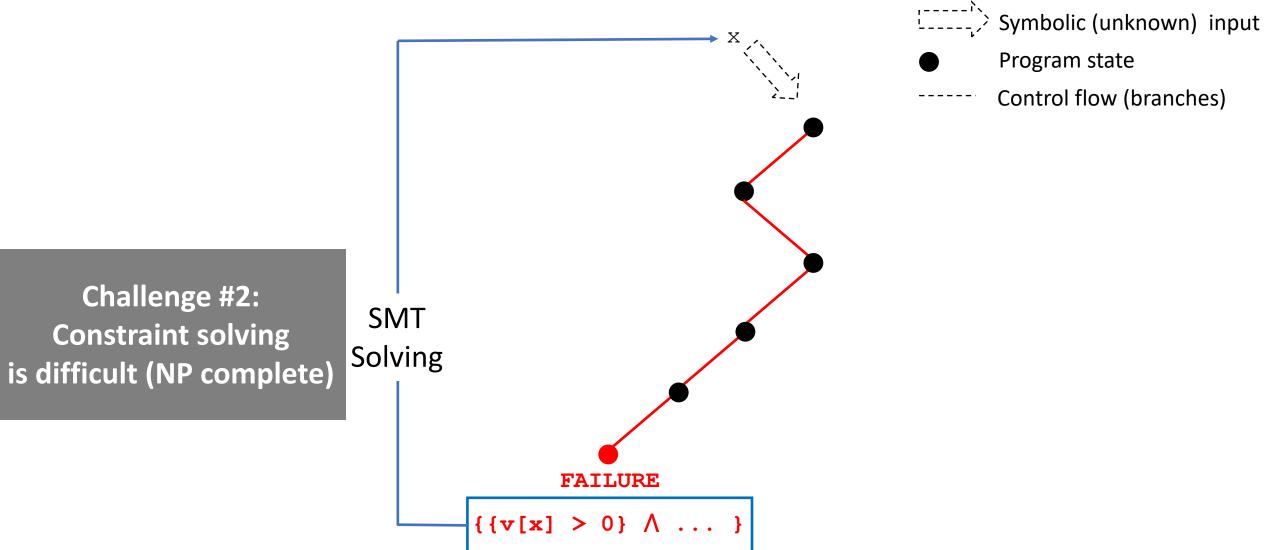

- Avoids path-explosion by following a control flow trace recorded in production

- Reduces (simplifies) constraints using key data values recorded in production

#### Key question: What data values best simplify constraint solving?

# Constraint Simplification: Intuition

- SMT solving is a hard problem (NP-Complete)

- **Observation**: reasoning about memory aliasing takes the most time

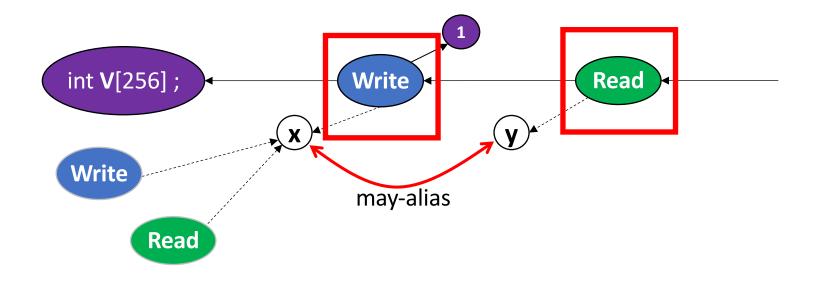

Memory Addresses: **x** may-alias **y**

Symbolic Memory

# Constraint Simplification: Intuition

- SMT solving is a hard problem (NP-Complete)

- **Observation**: reasoning about memory aliasing takes the most time

Memory Addresses: x may-alias y

Symbolic Memory

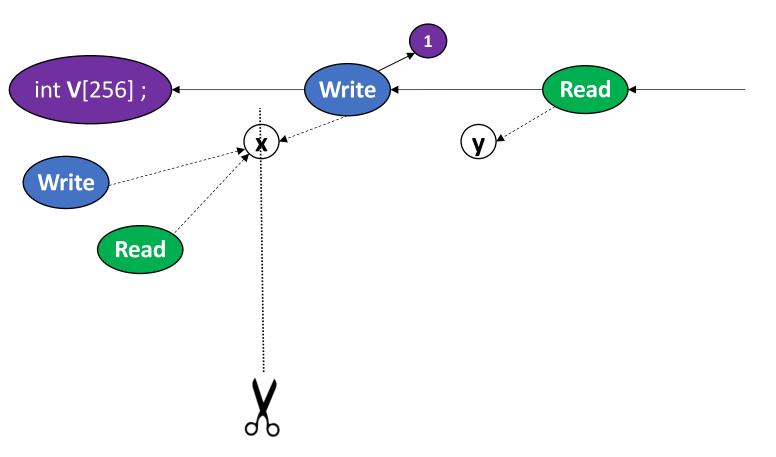

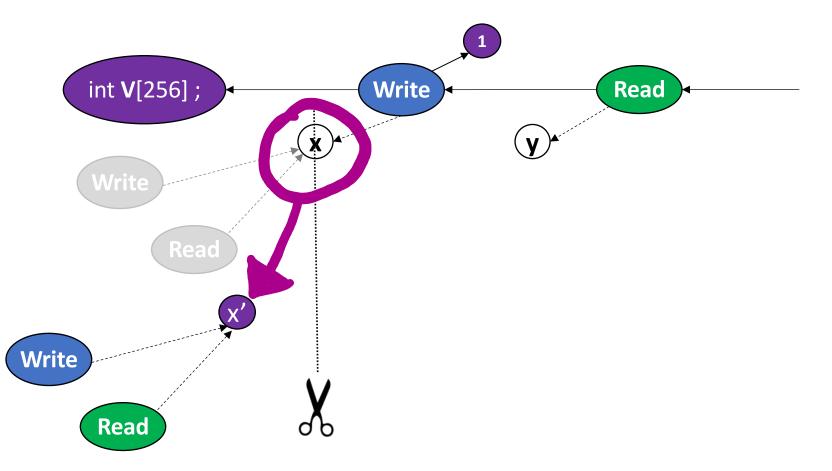

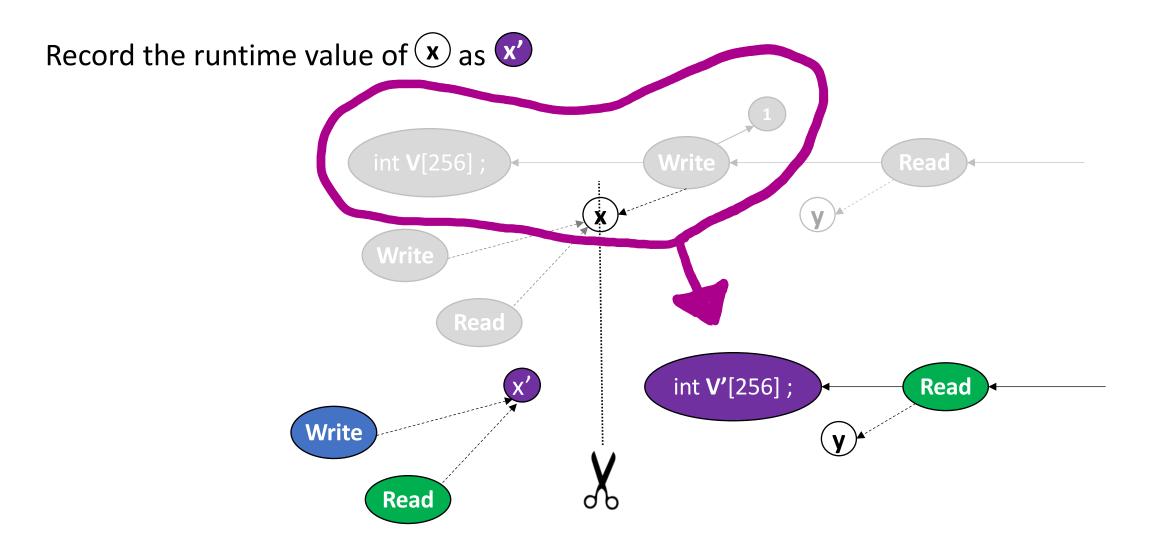

## Hypothesis: Recording addresses can simplify constraint solving

Record the runtime value of  $\bigotimes$  as  $\bigotimes$

Record the runtime value of  $\mathbf{x}$  as  $\mathbf{x}$

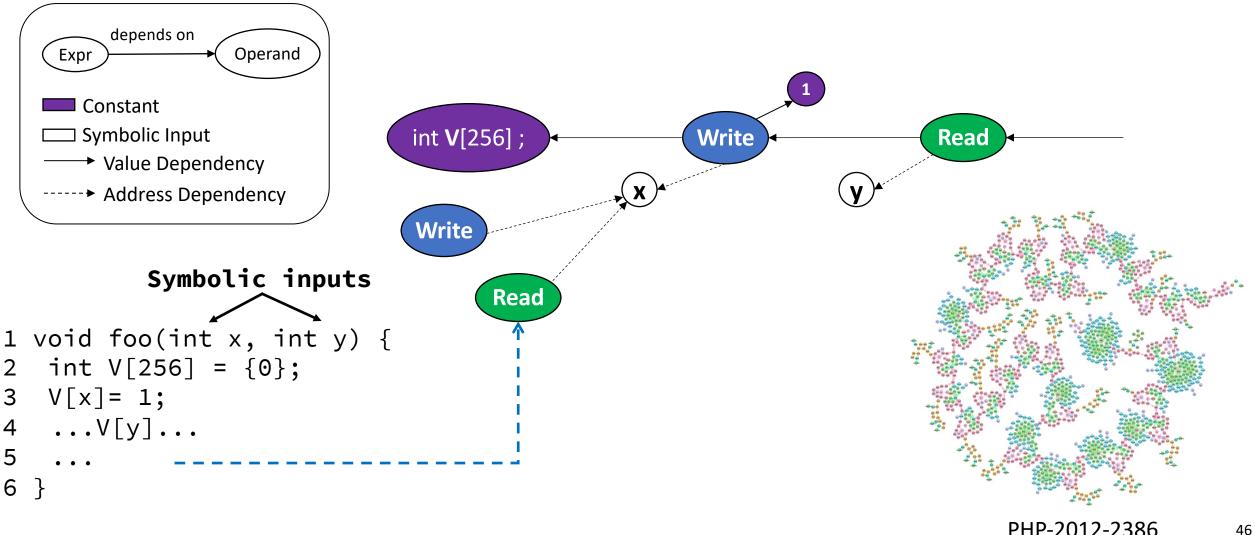

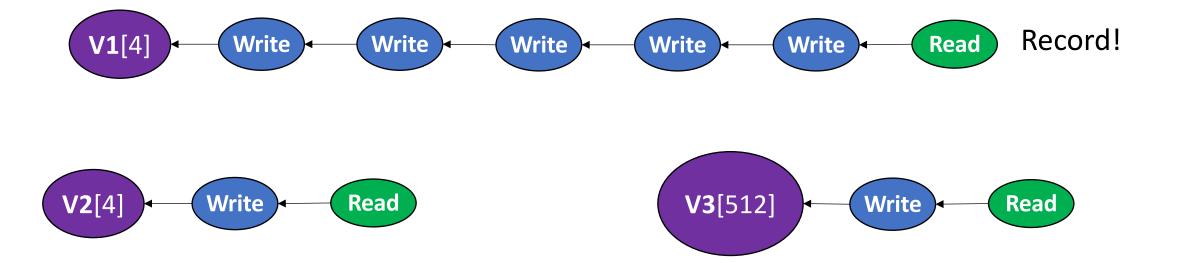

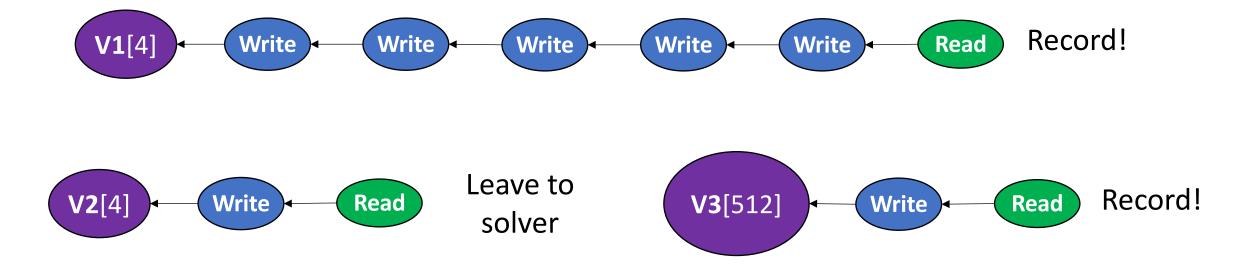

# Constraint Simplification: Heuristics

Record "key" symbolic memory addresses, which are used in:

- The longest symbolic write chain

- The write chain that accesses the largest symbolic memory object

# Constraint Simplification: Heuristics

Record "key" symbolic memory addresses, which are used in:

- The longest symbolic write chain

- The write chain that accesses the largest symbolic memory object

# **Execution Reconstruction Summary**

# **Execution Reconstruction Summary**

Reproduces O(10<sup>4</sup>) instructions Reproduces O(10<sup>7</sup>) instructions

# Execution Reconstruction – Results

Eliminates path explosion & simplifies constraint solving

• By recording control flow and key data values

Can reproduce failures in complex, long-running executions

- 1000x longer than REPT (deployed in Windows), without recording a longer trace

- Requires only 3.5 reoccurrences on average per failure

0.3% runtime performance overhead

#### Failure Reproduction and Analysis OmniTable [OSDI'22]

Debugging in the Brave New World [ASPLOS'22] ER [PLDI'21] REPT [OSDI'18] Snorlax [SOSP'17]

Hippocrates [ASPLOS'21] Agamotto [OSDI'20]

# Microsoft vmware<sup>®</sup>

#### Awards

NSF CAREER Award

Microsoft Research Faculty Fellowship Google Faculty Award

- 2019, 2021 Microsoft Research PhD Fellowship

- Andrew Quinn

NSF Graduate Research Fellowship

• Andrew Loveless, Andrew Quinn

Towner Prize

Ian Neal

OSDI Best Paper Award

IEEE MICRO Top Pick Honorable Mention

#### Grants

NSF, SRC, Google

#### **Collaborations**

UT Austin, KAIST, Intel

#### **Real-world deployment in Windows**

~1 billion systems

#### Adoption at Meta<sup>1</sup>, Intel

[1] https://engineering.fb.com/2021/04/27/developer-tools/reverse-debugging/ 57

# Outline

|                                   | Offline                            | Online                              |

|-----------------------------------|------------------------------------|-------------------------------------|

| Datacenter Efficiency             | Data-driven<br>optimizations       | Lightweight<br>profiling            |

|                                   | Static & symbolic                  | Coloctivo                           |

| Failure Reproduction and Analysis | Static & symbolic program analysis | Selective<br>information monitoring |

# Outline

|                                   | Offline                            | Online                             |

|-----------------------------------|------------------------------------|------------------------------------|

| Datacenter Efficiency             | Data-driven<br>optimizations       | Lightweight profiling              |

| Failure Reproduction and Analysis | Static & symbolic program analysis | Selective information monitoring   |

| Hardware Security                 | Classification<br>of attacks       | Threat model-<br>specific defenses |

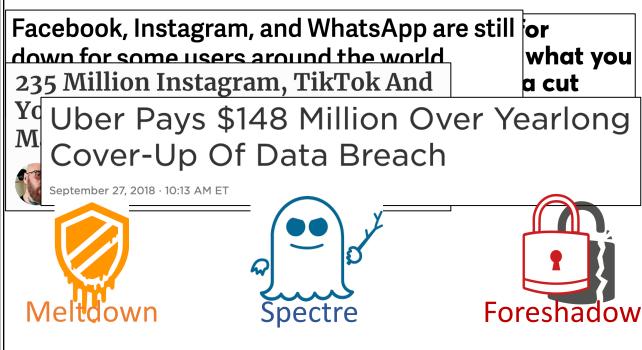

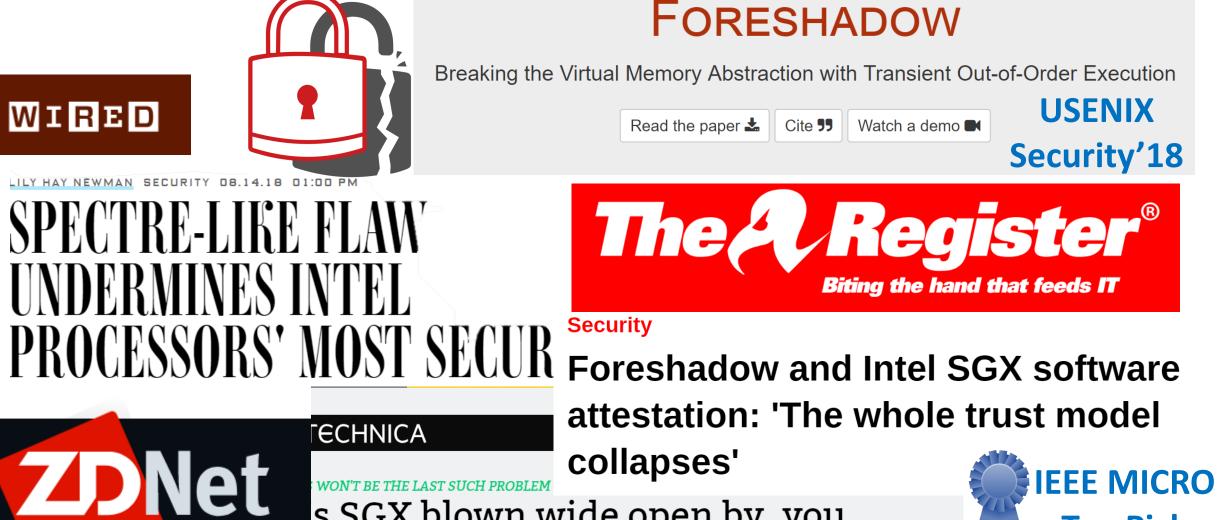

Foreshadow bypasses the virtual memory abstraction: A VM in the Cloud can leak secrets from someone else's VM

s SGX blown wide open by, you

sed it, a speculative execution attack

**Top Pick**

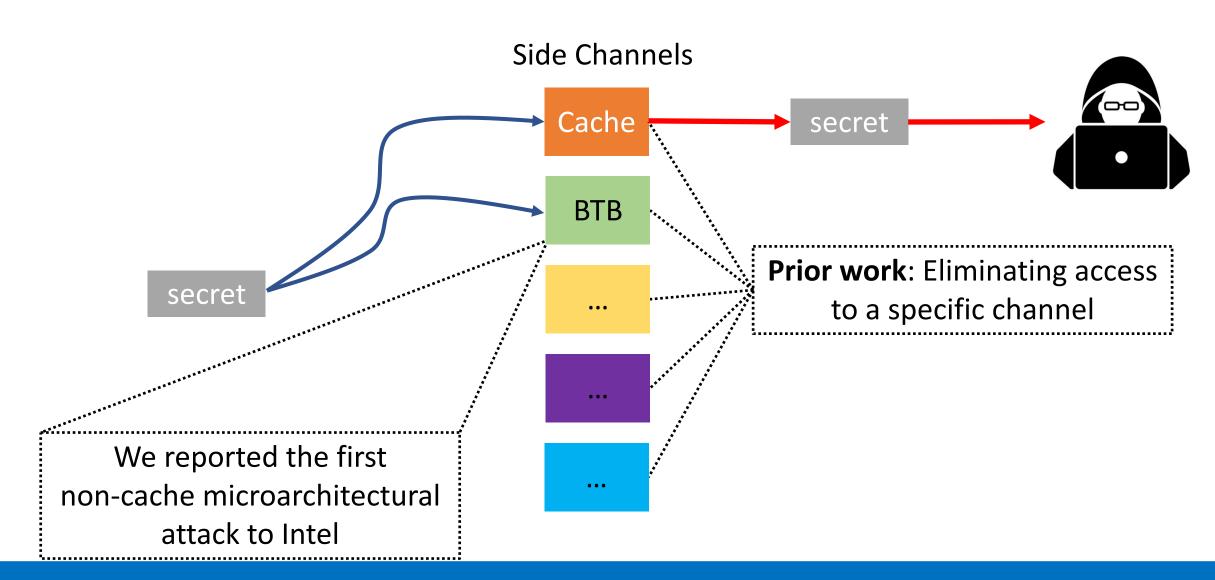

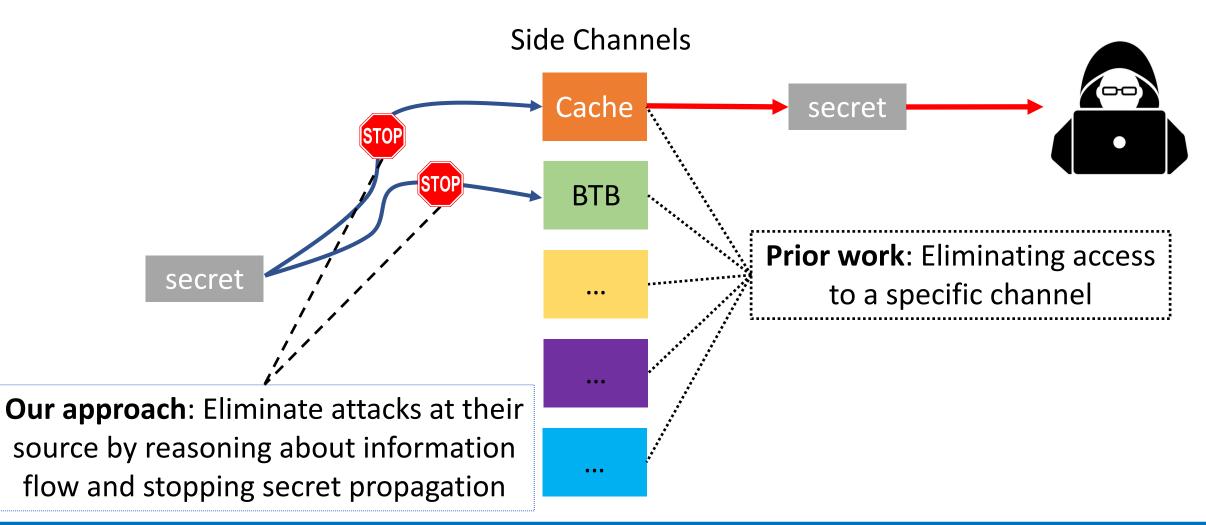

#### Prior defenses were channel-specific

# Principled and Comprehensive Defenses

Navigating the efficiency/trustworthiness tension: defenses tailored to threats

#### NDA: Preventing Speculative Execution Attacks at Their Source

Ofir Weisse University of Michigan Ian Neal University of Michigan Kevin Loughlin University of Michigan

Thomas F. Wenisch University of Michigan Baris Kasikci University of Michigan

IEEE Micro Top-Pick Honorable Mention

**MICRO'19**

# NDA's Key Insight

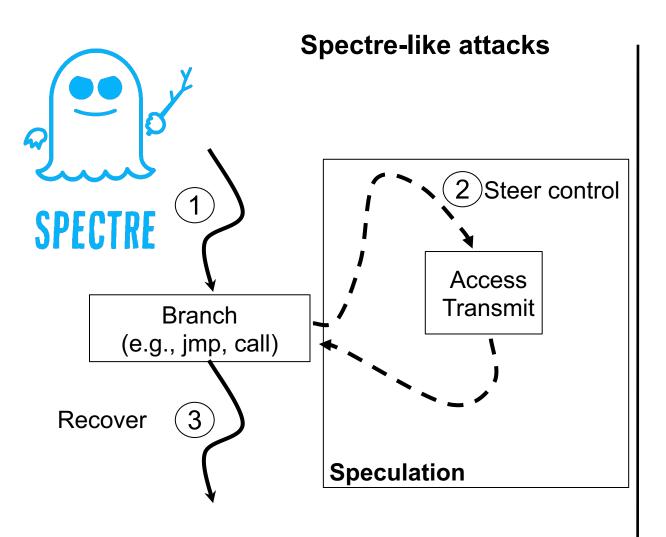

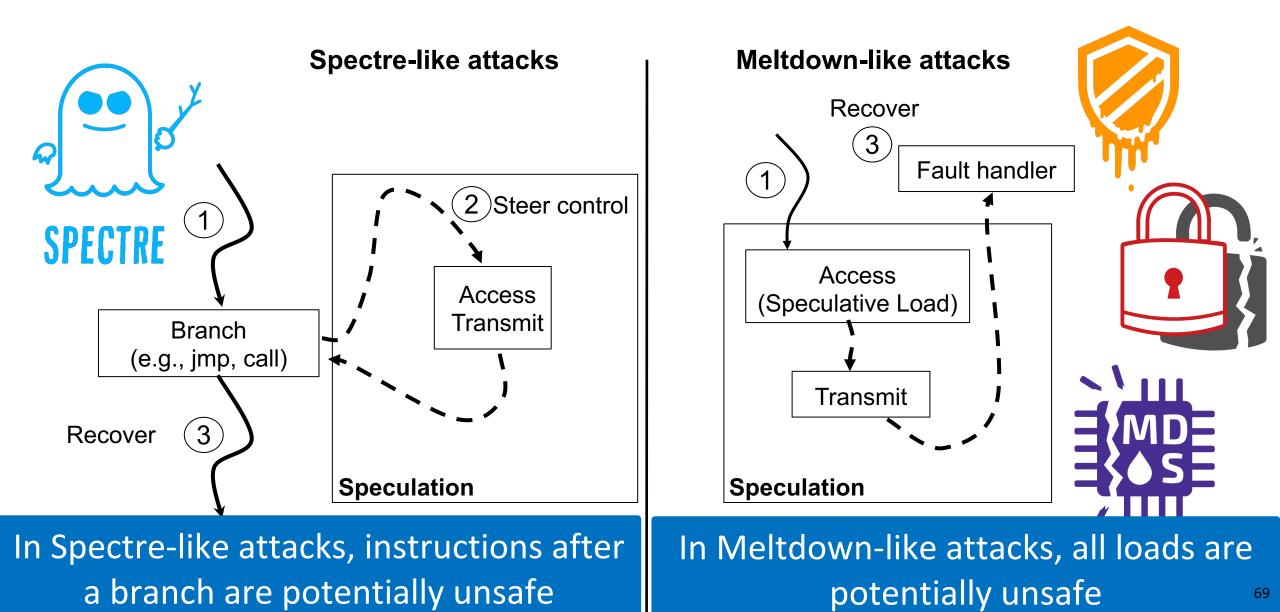

Speculative execution attacks require a chain of **dependent instructions** to access and transmit secrets.

By controlling data propagation, NDA can **break these dependency chains**, thwarting the code sequences required to mount attacks.

Analysis of Attacks: A Chain of Dependent Instructions

I) Access Phase **During speculation II)** Transmit Phase e.g., via the cache **III) Recover Phase** using timing After speculation measurements

# Analysis of Attacks: A Chain of Dependent Instructions

I) Access Phase

**II) Transmit Phase** e.g., via the cache

NDA can **break** the chain of dependent instructions

Only "unsafe" instructions are not allowed to speculatively transmit secrets

# Unsafe Instructions: A Threat-Model-Centric View

# Unsafe Instructions: A Threat-Model-Centric View

# NDA - Summary

During speculation, NDA:

- Allows the execution of unsafe instructions (access)

- Disallows broadcasting the effects of unsafe instructions (transmission)

Much lower overhead than in-order execution (4.8x)

- 10.7% overhead against Spectre-like attacks

- 36.1% overhead against Meltdown-like attacks

More comprehensive security than channel-specific defenses

• Protection against existing and future side-channels

## Hardware Security MOESI-prime [ISCA'22] Dolma [SEC'21] NDA [MICRO'19] Foreshadow [SEC'18] Morpheus [ASPLOS'19]

# ence & Technology

#### Awards

#### Facebook Fellowship

Marina Minkin

#### NSF Graduate Research Fellowship

• Kevin Loughlin

Google Fellowship

• Kevin Loughlin

**IEEE MICRO Top Pick**

IEEE MICRO Top Pick Honorable Mention

#### Grants

DARPA, ONR

#### **Collaborations**

Microsoft, KU Leuven, Technion, University of Adelaide

Improved cloud security

**Processor upgrades and patches**

# Future Work

# Data trends will continue driving software complexity up

Increased heterogeneity, new interconnects, and more edge devices will bring entirely new efficiency and trustworthiness challenges

Exploring emerging computer systems problems through the lens of computer architecture, programming languages, and security 72

# Data Center Efficiency

## Trends

Increasing memory, compute, and interconnect heterogeneity

• Multi-tier memory, specialized hardware, diverse interconnects

## **Future Work**

#1: Rethinking profile-guided optimizations (via HW/SW co-design) for heterogeneous systems

# Data Center Efficiency

## Trends

Increasing memory, compute, and interconnect heterogeneity

• Multi-tier memory, specialized hardware, diverse interconnects

## **Future Work**

#1: Rethinking profile-guided optimizations (via HW/SW co-design) for heterogeneous systems

#2: Designing new systems abstractions for resource management in a disaggregated environment

# Reliability

## **Trends**

Increased heterogeneity and hardware specialization

Always-on profiling/monitoring on the edge and datacenter

• Primarily used for performance optimizations

## **Future Work**

#1: Using production data to rethink our approach to trustworthiness

# Reliability

## **Trends**

Increased heterogeneity and hardware specialization

Always-on profiling/monitoring on the edge and datacenter

• Primarily used for performance optimizations

## **Future Work**

#1: Using production data to rethink our approach to trustworthiness

#2: Techniques for building more reliable heterogeneous systems<sup>1</sup>

[1] Debugging in the Brave New World of Reconfigurable Hardware. Jiacheng Ma, Gefei Zuo, Kevin Loughlin, Andrew Quinn, <u>Baris Kasikci</u>. ASPLOS 2022

# Hardware Security

## Trends

Microarchitectural isolation is a recurring problem Increased intermittent and silent hardware errors<sup>1,2</sup>

## **Future Work**

## #1: Microarchitectural isolation as a foundational security primitive

[1] Cores That Don't Count, Peter H. Hochschild Paul Jack Turner Jeffrey C. Mogul Rama Krishna Govindaraju Parthasarathy Ranganathan David E Culler Amin Vahdat Proc. HotOS 2021

[2] Silent Data Corruptions at Scale, Harish Dattatraya Dixit, Sneha Pendharkar, Matt Beadon, Chris Mason, Tejasvi Chakravarthy, Bharath Muthiah, Sriram Sankar, Arxiv, 2021

# Hardware Security

## **Trends**

Microarchitectural isolation is a recurring problem Increased intermittent and silent hardware errors<sup>1,2</sup>

## **Future Work**

#1: Microarchitectural isolation as a foundational security primitive

## #2: Techniques for eliminating/reducing hardware errors<sup>3</sup>

[1] Cores That Don't Count, Peter H. Hochschild Paul Jack Turner Jeffrey C. Mogul Rama Krishna Govindaraju Parthasarathy Ranganathan David E Culler Amin Vahdat Proc. HotOS 2021

[2] Silent Data Corruptions at Scale, Harish Dattatraya Dixit, Sneha Pendharkar, Matt Beadon, Chris Mason, Tejasvi Chakravarthy, Bharath Muthiah, Sriram Sankar, Arxiv, 2021

[3] Preventing Coherence-Induced Hammering in Commodity Workloads. Kevin Loughlin, Stefan Saroiu, Alec Wollman, Yatin Manerkar, **Baris Kasikci**, ISCA'22

## Efficiency

## Trustworthiness

|                     | Datacenter Efficiency                          |          |                                 |  |  |

|---------------------|------------------------------------------------|----------|---------------------------------|--|--|

| V                   | Whisper [MICRO'22] 📯 Thermometer [ISCA'22]     |          |                                 |  |  |

|                     | Twi                                            | g [MICRO | 21] PDede [MICRO'21]            |  |  |

|                     | DN                                             | lon [OSD | <sup>21]</sup> I-SPY [MICRO'20] |  |  |

| F                   | Ripple [ISCA'21] Huron [PLDI'19] Cntr [ATC'18] |          |                                 |  |  |

| ·····               | Heterogeneous Systems Support                  |          |                                 |  |  |

|                     | Persistent Memory Indexing [FAST'21]           |          |                                 |  |  |

| Optimus [ASPLOS'20] |                                                |          |                                 |  |  |

|                     | Systems                                        | Security |                                 |  |  |

|                     | Architecture                                   | PL       |                                 |  |  |

## **Failure Reproduction and Analysis** OmniTable [OSDI'22]

Debugging in the Brave New World [ASPLOS'22]

ER [PLDI'21] REPT [OSDI'18] Snorlax [SOSP'17]

Hippocrates [ASPLOS'21] Agamotto [OSDI'20] 📿

**Verified Distributed Systems**

Sift [ATC'22] IGOR [RTAS'21]

14 [SOSP'19]

Hardware Security

MOESI-prime [ISCA'22]

Dolma [SEC'21]